#### LIMITED WARRANTY

> Ohio Scientific, Inc., 1333 S. Chillicothe Rd., Aurora, Ohio 44202 (the "Warrantor") hereby warrants to the original purchaser that its hardware equipment will be free from defects in materials and workmanship for a period of ninety (90) days from the date of receipt by purchaser when operated and maintained in accordance with Ohio Scientific's recommendations. This warranty includes power supplies and floppy disk drives. It specifically excludes terminals, video monitors, audio cassettes and keyboards not manufactured by Ohio Scientific.

Ohio Scientific warrants its software against media that is defective such that it is not readable by the computer system for a period of ninety (90) days from the date of receipt by purchaser. The software is thoroughly tested and thought to be reasonably bug-free when released. Ohio Scientific maintains a full staff of software experts and will endeavor to correct any serious bugs that may be discovered in the software after release in a resonable amount of time. However, this is a statement of intent and not a warranty or guarantee in such event. (Software sold with annual site licenses offer additional support commitments. See their contracts for details.)

You must have purchased the product from a duly authorized Ohio Scientific dealer whose name appears in Ohio Scientific's current dealer listing to qualify for the 90 day warranty. Ohio Scientific makes no other express warranty than that made above. Any implied warranty, including but not limited to the implied warranty of MERCHANTABILITY or fitness for a particular purpose, shall not be extended beyond the ninety (90) day period.

Ohio Scientific's obligation under the above warranty is limited to the repair of the product, without charge, if it is defective and has not been misused, carelessly handled, or defaced by repairs made or attempted by others and it is returned to Ohio Scientific for repair. Ohio Scientific shall not be liable for any other loss or damage resulting directly or indirectly from the defect in the product including, but not limited to, incidental or consequential damages for lost profits, lost sales, injury to person or property, or any other incidental or consequential loss.

In the event that you desire to obtain performance of any warranty obligation, please return the product in its original or other adequate packaging to Ohio Scientific, Inc. or by prior arrangement to the dealer from whom you purchased the unit.

Ohio Scientific reserves the ultimate authority to determine what constitutes in-warranty repair in circumstances where circuit modification, abuse, misuse, or shipping damage occurs. If it is determined that the product is not under warranty, it will be repaired using Ohio Scientific's standard rates for parts and labor. Ohio Scientific will use its best efforts to repair the product within three weeks after receipt thereof. However, Ohio Scientific shall not be responsible for delays beyond its control such as, but not limited to, those caused by shipping or long delivery of replacement components.

The warranty contained herein is the only warranty which any Ohio Scientific dealer is authorized to give in conjunction with the product. Ohio Scientific shall not be bound by any other warranty made by the dealer to the purchaser. The support of such warranty or maintenance contract is the sole responsibility of the dealer offering the warranty.

When requesting performance under the terms of this warranty, the original purchase date or date of purchaser's receipt of the product must be established by means of a bill of sale, invoice, or other acceptable documentation.

This warranty gives you specific legal rights, and you may also have other rights which vary from state to state.

If there are any questions about this warranty, or if a complaint has not been answered by the dealer to your satisfaction, please contact:

OHIO SCIENTIFIC, INC. 1333 S. Chillicothe Rd. Aurora, Ohio 44202 Attn: Warranty Information

# WARRANTY INFORMATION

/

|   | Name Phone ( )                                                      |                                                       |                                  |  |  |  |  |  |  |  |  |  |

|---|---------------------------------------------------------------------|-------------------------------------------------------|----------------------------------|--|--|--|--|--|--|--|--|--|

|   | Street                                                              |                                                       |                                  |  |  |  |  |  |  |  |  |  |

|   | City                                                                | State                                                 | Zip                              |  |  |  |  |  |  |  |  |  |

|   | Purchased from                                                      | Date of purc                                          | hase                             |  |  |  |  |  |  |  |  |  |

|   | Model Number                                                        | Serial Number                                         |                                  |  |  |  |  |  |  |  |  |  |

|   | (see nameplate on back)                                             |                                                       |                                  |  |  |  |  |  |  |  |  |  |

| • | Please complete the following ad<br>may be better able to meet your |                                                       |                                  |  |  |  |  |  |  |  |  |  |

|   | Age                                                                 | Peripherals (                                         |                                  |  |  |  |  |  |  |  |  |  |

|   | Education ( ) high school                                           | purchased (<br>(                                      | ) printer<br>) other             |  |  |  |  |  |  |  |  |  |

|   | ( ) college<br>( ) graduate                                         | Where you learn                                       | ed of OSI                        |  |  |  |  |  |  |  |  |  |

|   | Occupation                                                          | ( ) friend                                            |                                  |  |  |  |  |  |  |  |  |  |

|   | Use of computer ( ) home                                            | <ul><li>( ) magazine</li><li>( ) trade show</li></ul> |                                  |  |  |  |  |  |  |  |  |  |

|   | () business<br>() school                                            | ( ) dealer<br>( ) other                               |                                  |  |  |  |  |  |  |  |  |  |

|   | Software purchased? ( ) yes<br>( ) no                               | Plans to expand                                       | system ( ) yes<br>( ) no         |  |  |  |  |  |  |  |  |  |

|   | Type of software                                                    |                                                       |                                  |  |  |  |  |  |  |  |  |  |

|   | Additional software desired but                                     | not available                                         |                                  |  |  |  |  |  |  |  |  |  |

|   | Was dealer helpful? ( ) yes<br>( ) no                               | Does he carry fu<br>accessories?                      | ull line of<br>( ) yes<br>( ) no |  |  |  |  |  |  |  |  |  |

|   |                                                                     |                                                       |                                  |  |  |  |  |  |  |  |  |  |

|   | Please mail this completed form                                     | upon receipt of yo                                    | our computer to:                 |  |  |  |  |  |  |  |  |  |

|   | 1333 S. C                                                           | NTIFIC, INC.<br>hillicothe Rd.<br>hio 44202           |                                  |  |  |  |  |  |  |  |  |  |

|   |                                                                     | rranty Information                                    | -                                |  |  |  |  |  |  |  |  |  |

# TABLE OF CONTENTS

•

ſ

# CA-22 Analog Input Output Interface Operation Manual

| AN INTRODUCTION TO THE OHIO SCIENTIFIC SIXTEEN PIN I/O BUS                                                                                                                                                               | נ                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| CA-15 Board<br>CA-20 Board<br>HEAD END CARDS<br>Bit Switching and Sensing — The CA-21<br>EPROM Programmer — The CA-23<br>Prototyping — The CA-24<br>Accessory Interface — The CA-25<br>Analog I/0 — The CA-22<br>Summary | 1<br>2<br>3<br>4<br>5<br>7<br>8<br>7<br>8<br>1<br>1 |

| CA-22 Overview                                                                                                                                                                                                           | 12                                                  |

| Logic Control Inputs/Outputs<br>X-Y Scope Plotting<br>HEAD END CARD or Motherboard Installation<br>Artwork Conveniences<br>Summation<br>Software<br>Audio Demonstration                                                  | 14<br>14<br>15<br>15<br>18<br>21                    |

| Applications Information                                                                                                                                                                                                 | 28                                                  |

| D/A Converters<br>A/D Converter<br>Scaling<br>Digital Input Codes<br>Digital I/O<br>X-Y Oscilloscope Plotting<br>Adjustments                                                                                             | 28<br>28<br>31<br>31<br>34<br>35<br>36              |

| D/A Offset Adjustments<br>D/A Gain Adjustments<br>A/D Offset Adjustment<br>A/D Gain Adjustment                                                                                                                           | 36<br>36<br>36<br>36                                |

| Theory of Operation                                                                                                                                                                                                      | 38                                                  |

| Analog to Digital Data Acquisition<br>Digital to Analog Conversion                                                                                                                                                       | 38<br>40                                            |

| Installation                                                                                                             | 42                   |

|--------------------------------------------------------------------------------------------------------------------------|----------------------|

| Accessory Bus C4P-MF, C8P-DF<br>48-Pin Motherboard Bus Installation Backplane<br>Power Requirements<br>Power Connections | 42<br>46<br>50<br>50 |

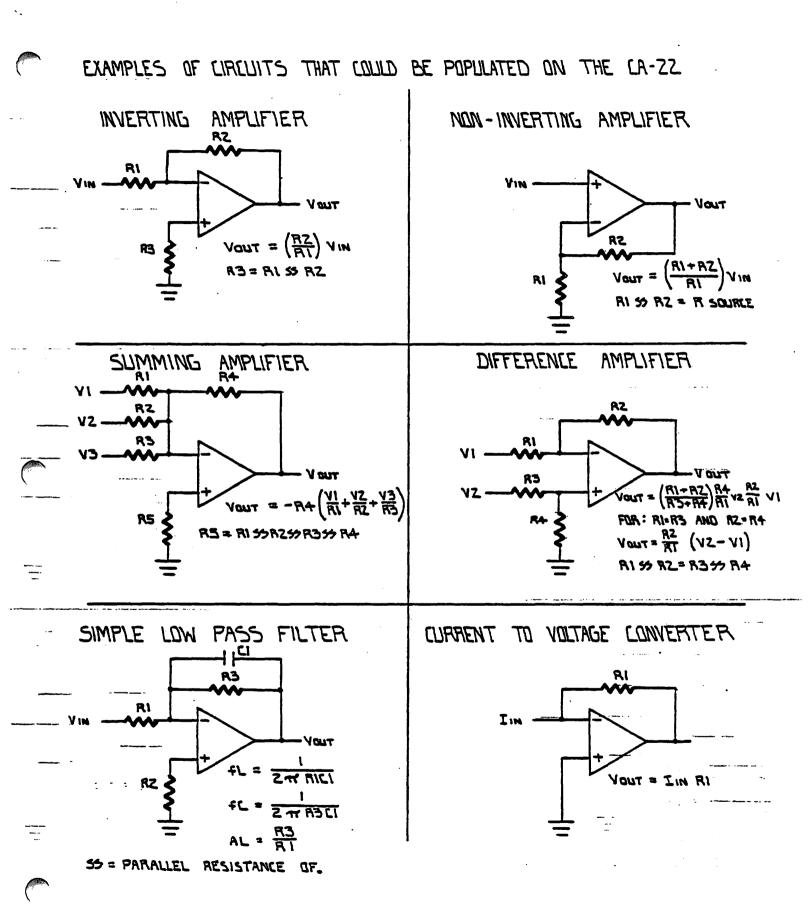

| EXAMPLES OF CIRCUITS THAT COULD BE POPULATED ON THE CA-22                                                                | 55                   |

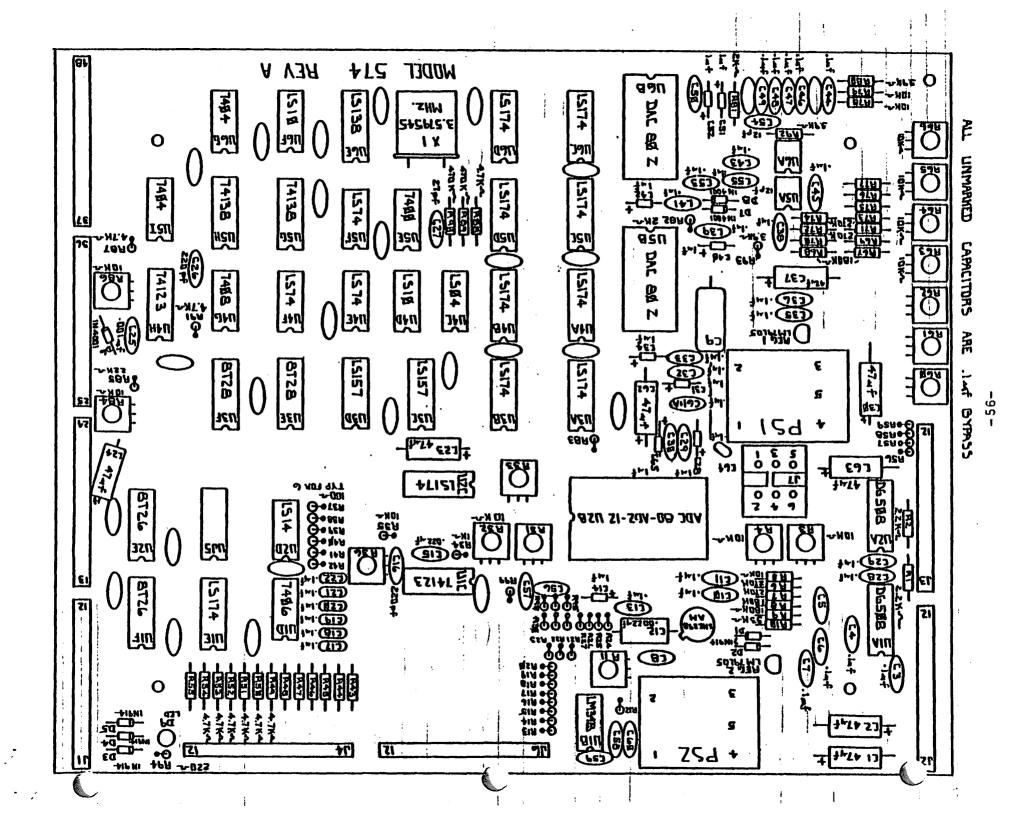

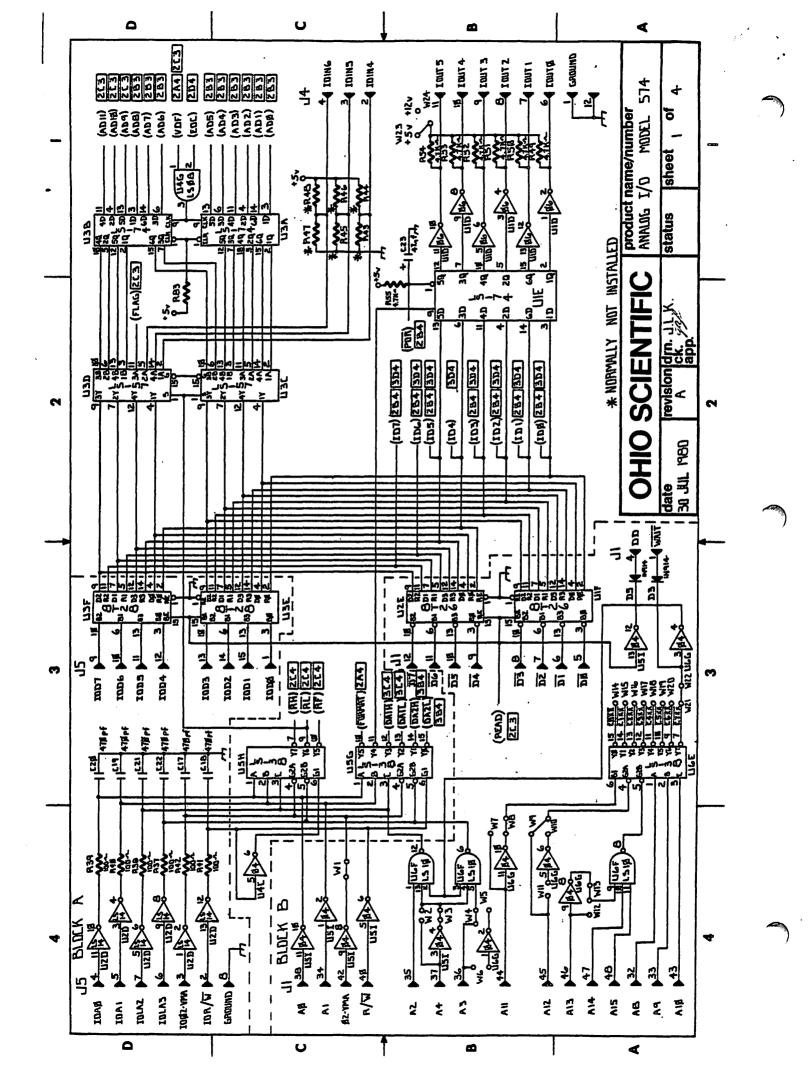

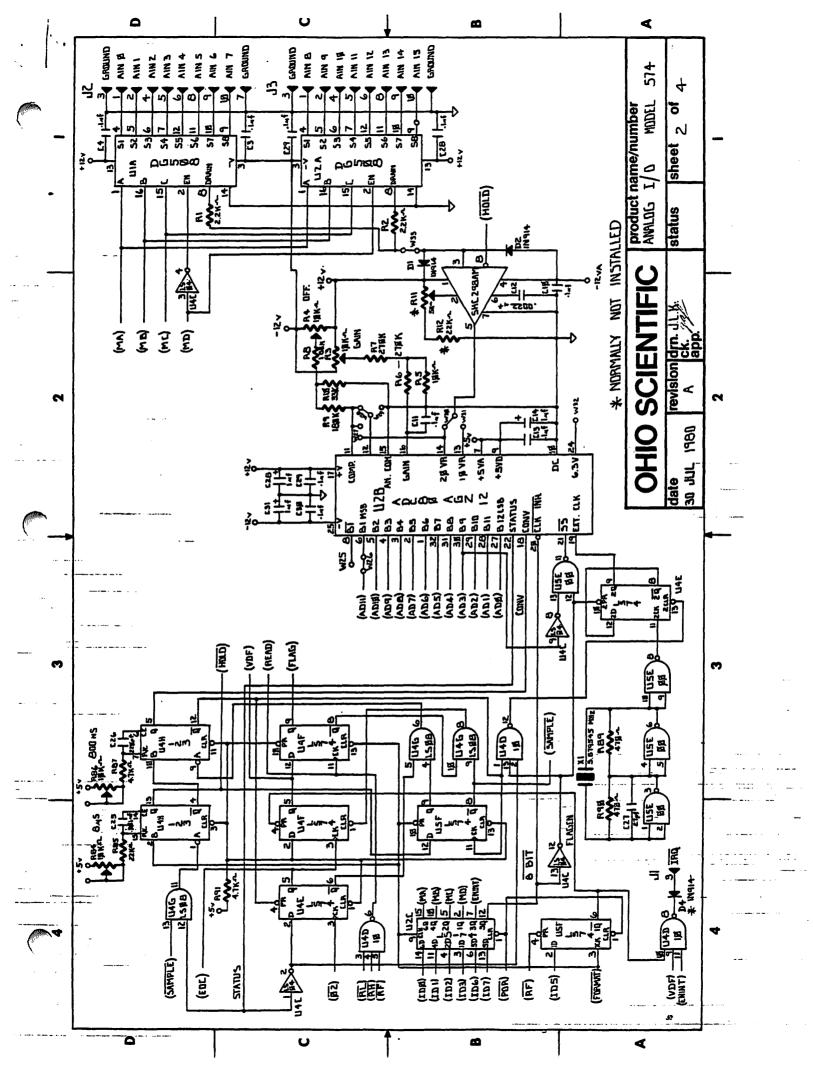

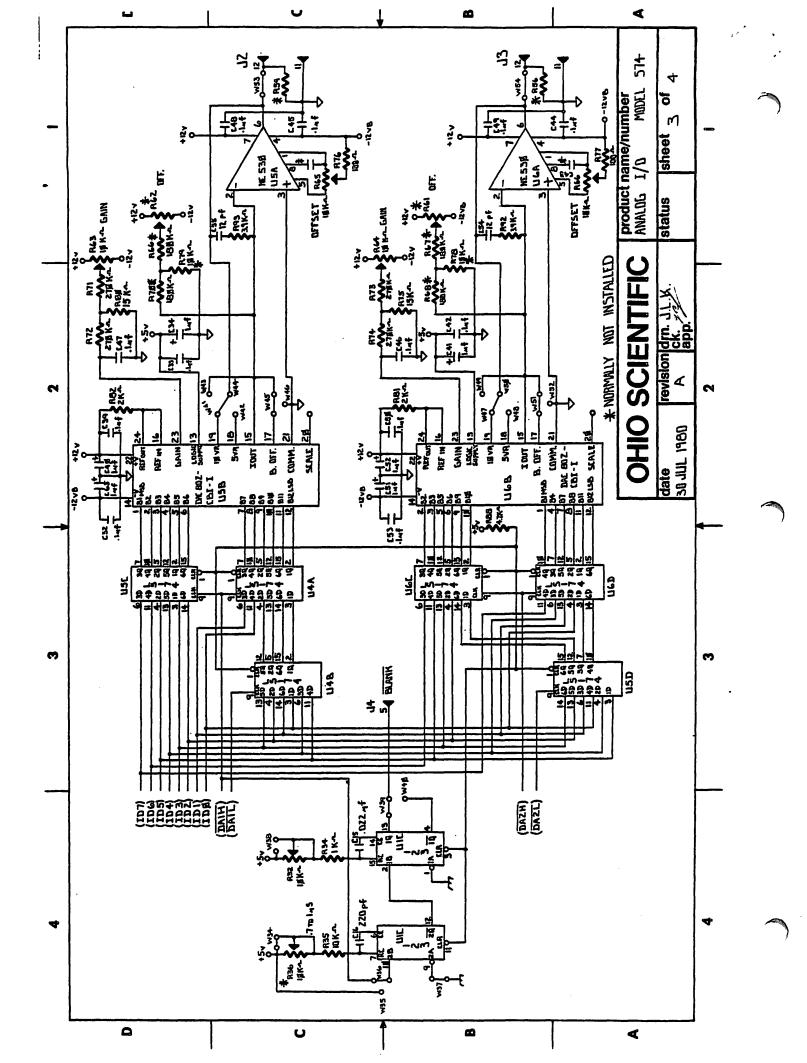

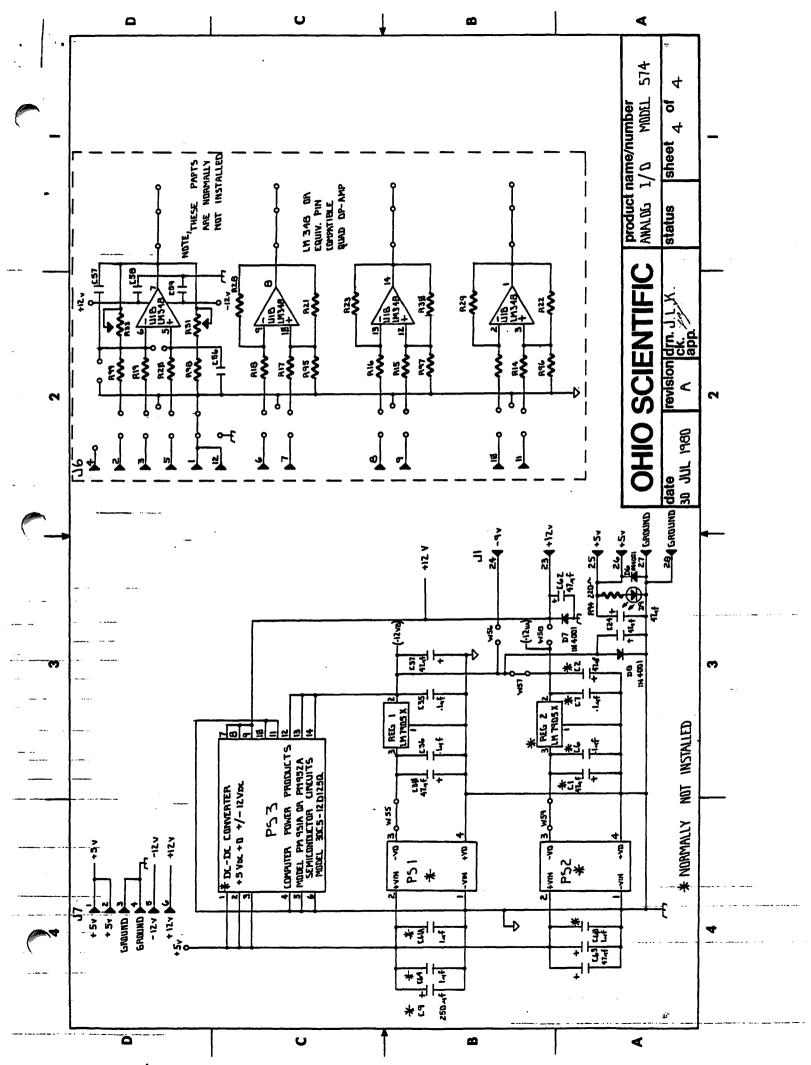

| BOARD LAYOUT, SCHEMATICS AND MANUFACTURERS' DATA                                                                         | 56                   |

•

.

4

AN INTRODUCTION TO THE OHIO SCIENTIFIC SIXTEEN PIN I/O BUS

Ohio Scientific is pleased to introduce a unique new product line - The 16 Pin I/O BUS. With this system, it is possible to add up to eight special function boards while occupying only the backplane slot.

This is made possible by a novel BUS extension method which allows decoding, timing and eight bits of data to be carried on standard, inexpensive 16 pin ribbon cables.

Up to eight inexpensive 16 pin cables with standard DIP connectors may be attached to a single CA-20 board which in turn occupies one slot of the standard Challenger backplane. Alternately, one 16 pin I/O BUS cable may be attached to the CA-15 board at the rear of all C4P and C8P products. Note, in the case of the C4P-MF this allows system expansion beyond the normal four slot backplane.

Currently five HEAD END CARDS are available for interconnection to the system via the CA-20 or CA-15 boards.

#### Computer Interface to Sixteen Pin I/O BUS

The 16 pin I/O BUS may be attached to your computer via two different boards - the CA-15 or the CA-20. The descriptions of these boards are as follows:

## CA-15 Board

The CA-15 board is a standard accessory interface installed on the following Ohio Scientific systems: C4P-MF, C4P-DMF, and C8P-DF.

The CA-15 is mounted at the rear of the computer and contains the following interface connections:

Joystick and numeric keypad Modem and serial printer Sixteen PIA lines (normally used for the Home Security system - AC-17P) Sixteen Pin I/O BUS

-1-

The interconnect for the Sixteen Pin I/O BUS is simply a 16 pin DIP socket. To use the BUS, all that you have to do is attach one end of the 16 pin ribbon cable to the CA-15 board and the other end of the cable to one of the HEAD END CARDS.

Please note that some of the HEAD END CARDS require more power than may be practically carried via the ribbon cable alone. Therefore, some of the cards require auxiliary power supplies. CA-20 Board

The CA-20 board contains all the necessary logic to decode eight distinct HEAD END CARD interfaces. The actual interconnect, as with the CA-15, is via simple 16 pin DIP sockets and standard 16 pin ribbon cables.

The CA-20 board also requires one slot of your computer's backplane. But remember, from this one slot you gain access to a maximum of eight accessory boards.

The CA-20 is recommended for use in the Ohio Scientific C2 series and C3 series computers. It can also be installed in C4P and C8P series systems with some modification to the CA-15 interface.

Since the logic required for the I/O BUS interface is simple, an additional feature was added to the CA-20 board - a crystal controlled "time-of-day" clock (hardware) subsystem. The operation of the clock, excepting reading time and setting time, is totally independent of the host computer. As a matter of fact, with the included on-board, auto-recharging, battery back-up, your computer may actually be turned off for several months without losing time.

-2-

The features of the clock subsystem are as follows: Hours, minutes, seconds and 1/10 seconds Day of week Day of month Month of year Four Year calendar

If you happen to own (or use) a C2 series or C3 series computer, the CA-20 board can actually control the power cycling of the entire computer when equipped with an optional power sequencer package. This means you can preset a time (month, day, hour, etc.) within the clock subsystem and when that preset time agrees with the actual time, A.C. power is applied to the entire computer system through the power sequencer. At a later time, the system's A.C. power may also be removed and the system shut down under software/clock subsystem control.

For applications where the clock subsystem is not required, the CA-20A will perform all the Sixteen Pin I/O BUS functions associated with full-feature CA-20.

#### HEAD END CARDS

HEAD END CARDS is a general name used to describe any or all of the special function boards which attach to the Ohio Scientific Sixteen Pin I/O BUS. There are currently five such boards and, with the exception of the CA-22, they will only interface with the computer via the Sixteen Pin I/O BUS.

Please note, as detailed earlier, you must use a CA-15 or a CA-20 board at the "computer end" of the Sixteen Pin I/O BUS to complete the interface.

-3-

In the following pages a brief product and application description of the currently available HEAD END CARDS will be presented.

# Bit Switching and Sensing ---- The CA-21

The CA-21 is a 48 line parallel I/O board featuring three 6821 PIAs (peripheral interface adapters) and prototyping/inter-

The use of PIAs in the design allows for maximum interface versatility as you may configure any one of the 48 I/O lines as either an input or an output. As outputs, each line is capable of driving a minimum of one standard TTL load.

Additional versatility is added because 24 of the lines, when configured as outputs, may simultaneously function as inputs. This feature, although somewhat confusing, is extremely useful for applications such as switch matrix decoding.

Each of the 48 lines is brought out to two foil pads (suitable for wire wrap stakes) as well as a location on one of four 12 pin Molex-type female edge connectors. There are also eight 16 pin DIP socket locations which are intended for use as prototyping areas. Additionally, the 12 PIA "hand-shaking" lines are brought to 12 single foil pads.

The CA-21, with proper buffering, may be used for virtually any computer controlled bit switching or bit sensing application that you can imagine. With a full complement of eight CA-21s interfaced via the CA-20, a total of 384 individually controllable I/O lines are possible!

-4-

An interesting application using one CA-21 board would be a complete, if somewhat slow, emulation of the standard Ohio Scientific BUS.

A more standard application might be augmenting the standard Home Security System (AC-17P) with "hard-wired" sensors.

One type of sensor you could easily add is a standard window "perimeter detector". This could be done with commercially available adhesive foil tape. You could then detect a break-in (through a broken window) by sensing a break in the foil tape.

Another useful application you could set up in concert with the AC-12P wireless A.C. Remote Control, might be sensing when a room is entered. You could accomplish this with pressureswitch door mats or door switches. When room entry is detected, the lights could be turned on or, turned off on exit.

If you are designing any sort of dedicated control system, the CA-21 is an ideal choice. You can easily sense many types of input (pressure transducers, flow sensors, switches, etc.) while controlling outputs from a simple single LED display to a network of solid state relays controlling A.C. power.

# EPROM Programmer ---- The CA-23

The CA-23 is an EPROM programmer designed for use with the growing families of 5 volt only EPROMS. With the CA-23 you can program and verify all 1K through 8K byte EPROMS of this type. Note these parts are often identified as 8K - 64K bit EPROMS.

The CA-23 can program (or verify) data in two basic modes -EPROM to/from EPROM or EPROM to/from computer RAM memory.

-5-

Additionally, EPROM data may be read directly into the computer's RAM memory.

There are four LED indicators on the CA-23. The first is "SOCKET UNSAFE". This means that a programming voltage is present at the socket and if you insert or remove an EPROM it is likely to be damaged.

The second indicator is "PROGRAMMING". This means that your EPROM is currently being programmed.

The third indicator is "ERROR". This means that somewhere along the line your programming attempt was unsuccessful.

The final indicator is "PROGRAM COMPLETE". This means that your program and verification was successful.

The most intriguing application for this product is the creation of "custom" parts for your computer or peripherals. This could range from a new system monitor to a new high level language. It could even include a new character generator for your CRT or printer. Note, however, tinkering around with the internals of computers and peripherals requires a fairly high degree of technical expertise. Also, most manufacturer's warranties are voided by these types of modifications.

Several OEM (original equipment manufacture) and Research/ Development applications will be immediately obvious to those of you involved in that work.

The CA-23, as previously mentioned, is designed for use with 1K through 8K byte EPROMS. These parts come in various package styles and have various product names. For example, Intel's 2K x 8 part is the 2716, Texas Instruments' part is known as the 2516.

-6-

The CA-23 has both 24 pin and 28 pin zero insertion force sockets for reading, programming and verifying the EPROMS.

# Prototyping ---- The CA-24

The CA-24 is a solderless bread-board designed for prototyping, experimental and educational applications.

The bread-boarding is made up of seven solderless plug-strips of the type manufactured by AP Products. Two of the plug-strips contain a connection matrix of 5 by 54 connections and are used as signal distribution points. Another pair of 96 location plug-strips are for powering the bread-board area. The actual experimenter area is comprised of three plug-strips, each with a 10 by 64 location connection matrix. Additionally, sixteen LED indicators and sixteen DIP switch positions are provided for signal observation and control functions.

Board I/O is via TTL latches and bi-directional PIA ports as well as direct (buffered) data, signal and control lines from the computer BUS. This method allows you to directly interconnect devices such as 6850 ACIAs in addition to doing more "isolated" and/or independent circuits.

The CA-24 also contains a "clock" generator which is continuously variable from approximately 25,000 Hz. through 70,000 Hz. You may also connect the clock to an on-board 16 stage divider chain. This allows division of the fundamental frequency by as little as  $2^1$  (2) to as much as  $2^{16}$  (65,536).

The applications for the CA-24 are primarily prototyping and experimenting. Parts may be inserted and removed from the

-7-

terminal strip blocks over and over. Interconnection of parts is accomplished simply with solid, narrow gauge wire jumpers. Errors in design or connection are extremely easy to correct.

The CA-24 lends itself very well to structured experiments that are common in the educational environment. It is an ideal tool to aid in the teaching of computer and computer interface fundamentals.

# Accessory Interface ---- The CA-25

The CA-25 is designed to implement some of the functions normally associated with the CA-15 interface board.

It allows you to directly connect the Home Security System (AC-17P) and/or the Wireless A.C. Remote Control System (AC-12P) to C2 and C3 series computers. Additionally, if you own an older Ohio Scientific computer, you can now easily connect these systems

An extremely useful application of the CA-25 is associated with small business systems. Using the CA-25 with the Home Security System, and perhaps a CA-15V (Universal Telephone Interface with speech synthesizer output), the computer could do payroll, inventory, etc. by day and "guard" the shop by night.

## Analog I/O ---- The CA-22

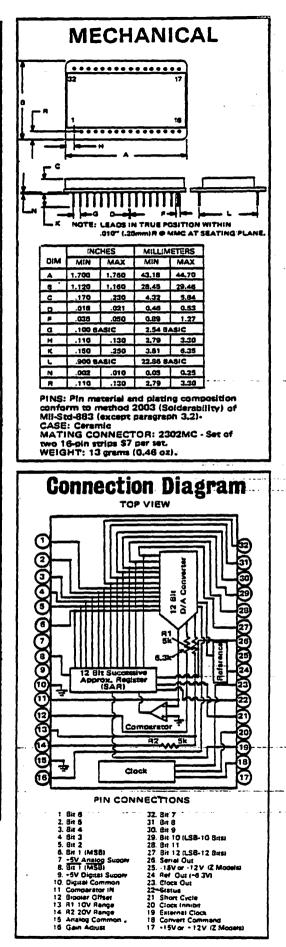

The CA-22 is a high speed analog I/O module. Although the CA-22 is classified as a HEAD END CARD, it differs from the rest of the family in that it may also be plugged directly into the computer's standard internal BUS. This allows for maximum flexibility in the use of the CA-22.

-8-

The analog input section of the CA-22 consists of a 16 channel amalog multiplexer. This means that you may connect up to 16 separate signals directly to the CA-22. Also included is a sample and hold circuit followed by the analog to digital converter circuitry.

The A to D converter is capable of either 8 bit or 12 bit operation. You may select these options under software control.

The accuracy of the converter is plus or minus one in the least significant bit. The stability of the circuit is rated at one millivolt drift per degree Centigrade.

The A to D conversion is extremely fast. It is capable of digitizing up to 66,000 samples per second in the 8 bit conversion mode and 28,000 samples per second in the 12 bit mode. Shannon Sampling Theory states that signals should be sampled at twice the highest frequency present. Therefore, it is possible for you to convert signals with a frequency greater than 30K Hz. Clearly, high fidelity audio is well within the spectrum of the CA-22.

The multiplexer has very high impedance inputs and is capable of accepting inputs in the range of -10 volts through +10 volts. The input is jumper selectable for other settings including a single sided range of 0 through +10 volts.

Due to the indeterminable nature of the actual inputs that you may actually apply to the CA-22, only the multiplexer inputs are brought out. However, a quad op-amp is laid out in foil which you may populate in several different modes to handle some of the more "common" input configurations.

-9-

The analog output section of the CA-22 consists of two identical high speed digital to analog converters. Each DAC can convert either 8 bits or 12 bits of data. Data input to the DACs is latched in such a manner that, when in the 8 bit conversion mode, the other four (of the total of twelve) bits are continuously output at a predefined value. You may, of course, define that value under software control.

The output of each DAC is buffered with a high speed opamp capable of changing output voltage at the rate of 20 volts per microsecond. The standard configuration of each output is bi-polar with a voltage swing of -10 volts through +10 volts. This is jumper selectable to allow a uni-polar output of 0 through +10 volts.

Some additional I/O capacity is provided on the CA-22. There are three TTL level inputs and six open collector logic outputs. These are strappable to be either standard TTL level outputs or high-voltage outputs.

You can use the CA-22 for a multitude of analog sensing and/or analog controlling applications.

Using the proper transducers and the 16 input channels, you can monitor the temperature in several zones of a home or office. By extending this system with a CA-21, you could maintain precise temperatures by switching the proper controls on and off.

Another interesting, if somewhat obvious application, is in audio processing. Reverberation, phase shifting and echoing are just a few of the uses you could implement.

-10-

If you used blocks of RAM for data storage, other applications such as frequency doubling, etc., could be experimented with.

If you apply more sophisticated software techniques, such as a fast Fourier transform, on stored input data, very elaborate signal processing becomes realizable. Projects such as audio spectrum analyzers and speech recognition experiments are certainly practical. Note, in these types of applications you are likely to find some signal pre-processing in hardware is certainly beneficial - if not totally necessary.

If you employ both DAC outputs and the on-board unblanking circuit, X-Y oscilloscope plotting is an interesting application. By using these techniques and one or more of the analog inputs, you can construct a digital storage scope. Note, both of these applications require that you have access to an oscilloscope capable of X-Y input as well as blanking.

#### Summary

With the introduction of the 16 pin I/O BUS, Ohio Scientific has opened a new world of interfacing capabilities for both the large and the small computer user.

Systems ranging from totally automated sampling and control stations to complete R/D setups to educational lab stations are now available to you via standard building blocks and standard computer systems.

For pricing and availability, contact your nearest Ohio Scientific dealer.

-11-

### CA-22

#### Overview

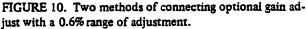

The analog I/O (input/output) board is a high performance analog to digital (A/D) and digital to analog converter (DAC) interface board with the following features:

16 channel (multiplexed) 12 or 8 bit A/D (analog to digital converter) with S/H (sample and hold) and very high impedance inputs. The CA-22 Analog I/O (input/output) provides the capability of converting up to 16 channels of continuous signals into discrete digital values which can be processed on your OSI computer. The user's program can scan one channel (PORT) continuously or all sixteen, or any combination, with each individual port selectively converted at 8 or 12 bit resolution, depending on the requirements of the application. High sampling rates with high resolution are available. A resolution of 12 bits (0.025% of full scale reading) or 8 bits (0.4% of full scale reading) may be selected. The software to control data acquisition is very simple and straightforward. Since the conversion is performed completely by the successive approximation type converter, no software conversion routines are required. The user's program need only instruct the CA-22 which port and at what resolution. This allows the processor complete freedom during the hardware conversion process to perform other tasks if required. This also allows the use of high level languages such as BASIC as well as machine code routines. The 16 port A/D is strappable to several unipolar (positive excursions from the ground reference) or bipolar (positive or negative excursions) to take full advantage

-12-

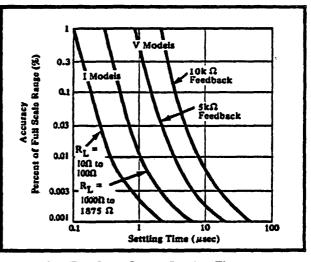

of the resolution of the converter. The maximum FSR (full scale range) is +10V to -10V (20V peak/peak) at 4.8 millivolt resolution per bit for 12 bit resolution (see chart, Figure 1, in another section of this manual for possible FSR ranges); 8 bit resolution of +/- 10 volts corresponds to 78 millivolt resolution.

Data and control are handled by use of dedicated addresses (device registers) which are treated as memory addresses. Additionally, three logical input lines and six logical output lines are provided on the J4 connector on the CA-22 board. These logical lines permit convenient interconnection to external circuits. The logic line data is also available in registers for normal programming.

The resolution of the CA-22 board is consistent with many process control and laboratory instrumentation demands; high fidelity audio processing can be easily accommodated with these capabilities.

Two 12 Bit D/A channels (digital to analog converters). Each D/A channel is identical and operates independently of the other. They may be operated directly in either the 8 bit or 12 bit mode at the discretion of the user depending on the resolution required. Each D/A may be independently strapped to several FSR ranges from 5V peak/peak to 20V peak/peak. The FSR range capability is identical to that of the A/D converter as is the bit resolution. Each D/A incorporates a current driven buffer for protection of the A/D and to provide very fast slew rates (voltage change vs time). Each D/A is capable of FSR

-13-

voltage swings (-10V to +10V) in less than two millionths of a second (2 microseconds) including switching, slewing and settling time.

# Logic Control Inputs/Outputs

Some applications may require logic control of the device the CA-22 is interfaced to, such as servo-drive direction and master enables, tape recorder control, or remote sensor enables. Six logic outputs and three logic inputs have been provided for this reason. The six outputs are latched, negative is true, buffered open collector drivers. These are configured as TTL compatible as shipped from the factory but can be strapped for higher voltage operation (up to 30V) by the user. The three inputs are TTL compatible with termination capability in artwork (user populated resistors).

### X-Y Scope Plotting

The CA-22 is provided with circuits to enable X-Y scope plotting by the user. The user must have access to an oscilloscope with X-Y inputs and an intensity or blanking input (usually found on the back of the scope). The two D/A converters provide the X-Y outputs and an output from the CA-22 (unblank) provides the blanking control. Many applications are possible using this technique including a digital or analog storage scope.

# HEAD END CARD or Motherboard Installation

The CA-22 is unique compared to other 'HEAD END CARDS' because it can be installed inside the computers card cage connected to the standard bus or outside of it on the OSI accessory bus for "hands on" use. See the installation section for more information.

-14-

#### Artwork Conveniences

In some applications the user may wish to pre-process the incoming analog information (filters, preamplifiers, summing amplifier, etc.) to lighten the load of the processor in "Real Time" or to decrease the complexity of the software required in advanced applications or experiments such as voice recognition, audio processing, etc. An area in artwork is included that provides the interconnections required to construct most of the typical op-amp circuits discussed. Also provided is a prototyping grid for digital or analog circuits the user may deem necessary for the application intended. Parts for these circuits are supplied by the user. Refer to other sections of this manual for more detail.

#### Summation

The CA-22 is a very accurate, fast analog interface module that can be used in a vast amount of different applications or experiments. The software to control the data acquisition is very simple and in some cases such as continuous (8) bit conversions of only one channel, the software need only read a location to obtain valid and continuously updated A/D information.

-15-

The A/D conversion rates 68,000 (8) bit or 28,000 (12) bit conversions per second and the accuracy (+/- 1LS) and the D/A conversion rate of full scale resolution swing in under two microseconds and an error of only (+/- 1LS) certainly would suggest many possible applications to the user. Some of these may be high fidelity audio processing, speech input/output lab, process control or home/business environmental control.

The conversion rates mentioned above are for single port conversion. The conversion rate of each channel when polling the ports will be slightly slower than the conversion rate divided by the number of ports polled. The above rates (68,000 - 8 bit or 28,000 - 12 bit) are a conservative figure. In actual practice the rates should be closer to 30,000 (12) bit and 70,000 (8) bit conversions per second, although these are not guaranteed. CA-22 I/0 ASSIGNMENTS

.--

| <u> </u> |       | _           | <b></b>             |             |            |          |            |          |

|----------|-------|-------------|---------------------|-------------|------------|----------|------------|----------|

| ø        | AD4   | ADØ         | MA                  | ourg        | D4         | DØ       | D4         | øa       |

| Ţ        | AD5   | AD1         | MB                  | OUTI        | D5         | D1       | D5         | Dl       |

| 2        | AD6   | AD2         | MC                  | OUT2        | D6         | D2       | D6         | D2       |

| З        | AD7   | AD3         | QW                  | <u>OUT3</u> | . D7       | D3       | D7         | D3       |

| 4        | AD8   | I/OIN4      | X                   | <b>OUT4</b> | D8         | X        | D8         | X        |

| 5        | AD9   | I/OIN5      | Ø=FLAG<br>ENABLE    | <u>ours</u> | <b>6</b> 0 | X        | 6 <b>0</b> | ×        |

| 9        | AD1Ø  | I/OIN6      | l=<br>En- Int       | ×           | DIØ        | X        | DIØ        | ×        |

| 7        | AD11  | 1=RDY       | 1=12 BIT<br>3=8 BIT | ×           | D11        | X        | D11        | ×        |

| REGISTER | DATA  | STATUS/DATA | CONTROL             | LOGIC OUT   | DAC1-HIGH  | DAC1-LOW | DAC2-HIGH  | DAC2-LOW |

| DECIMAL  | 5Ø952 | 56053       | 50954               | 5Ø955       | 5Ø956      | 5Ø957    | 5ø958      | 5Ø959    |

| HEX      | C7Ø8  | C7Ø9        | C7ØA                | с7øв        | င႗ဨင       | േള്വ     | C7ØE       | C7ØF     |

| R/W      | 'n    | R           | м                   | 3           | M          | м        | M          | 3        |

R/W = READ ONLY (R) OR WRITE ONLY (W)

SIG NAME = LOGIC OUTPUTS ARE LOW TRUE (\$=1)

¥\*

-17-

#### Software

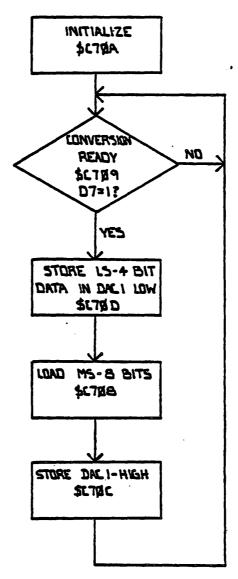

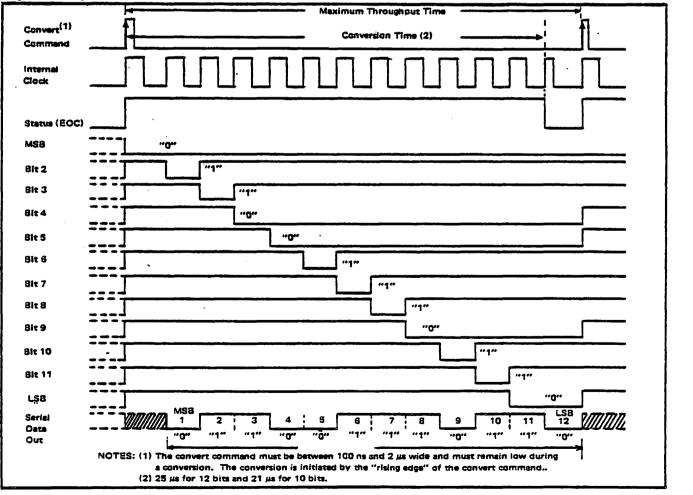

The analog to digital converter hardware is configured such that several different modes of data acquisition are available. A flag is provided that is used to inform the user that a new conversion is complete and updated data is available. This flag must always be used in the 12 bit mode and may or may not be used in the 8 bit mode at the discretion of the user.

The flag is necessary in 12 bit operation since a 12 bit word is being processed by an 8 bit machine. If the status register is read and the flag is valid the hardware sets an internal status register which prevents the data buffer from being modified until after the computer has read the second byte. Therefore, there are no timing considerations that must be observed in this operation other than the order of data acquisition which is the 4LSB's first and the 8 MSB second. The only other consideration in the flag mode is if one or all of the three TTL inputs (which are returned in the status register) are to be used, they must not be independently accessed. That is, the three inputs should be scanned only when reading the status register while looking for a data valid flag; when a valid data flag is returned the digital data can be masked from the analog data and immediately processed or stored. Repeatedly reading the status register, when the data conversion is complete, will result in the most significant bits of data being held constant, i.e. not being updated. For this reason, the sample program #1 is the preferred way to program.

-18-

If it is not required by the application, the flag circuitry may be turned off in the 8 bit mode. Reading the A/D information is then done simply by reading a location (\$C7Ø8).

Analog input port selection is done by writing to C70A. When scanning ports the flag mode should be used to insure an updated conversion of the selected port is complete. Bits MA to  $MD=\emptyset$  would select port  $\emptyset$  and bits MA to MD=15 would select port 15. If port 2 is to be read using the flag mode, the correct data to store at \$C7ØA would be \$Ø2 for 8 bit operating and \$82 for 12 bit operation. This value should be stored twice in immediate succession to force a new conversion of the new port. \$C709 would then be read checking D7 for a 1 or valid data flag. When the flag is received, the lower 4 bits of a 12 bit conversion are returned in  $D\emptyset-D3$  and in 8 bit conversions these 4 bits are simply ignored. Also during this time, the three TTL inputs are returned in D4-D6 of C709. The most significant (MS) 8 bits of a 12 bit conversion and the 8 bits of an 8 bit conversion are then simply reading \$C708. \$C708 will not be modified by the hardware until it has been read.

EX.1. 12 Bit Mode

Initialize the control register (\$C70A) to 12 bit, enable flag and select port (1X0XXXXX). When valid data is available, D7 of \$C709 will be a one. On the cycle that a valid data flag is received the least significant 4 bits of the conversion are returned in D3-D0, and the most significant 8 bits are available at \$C708, which are latched and will not be updated again until after \$C708 has been read.

#### EX.2. 8 Bit Mode With Flag

Initialize control register (C70A) to 8 bit, enable flag and select port (0X0XXXX). When valid data is available, D7 of C709 will be a one. After the valid data flag is read, the 8 bit conversion data is available at C708 and will not be updated until after it is read.

EX.3. 8 Bit Mode No Flag

Initialize control register (\$C7ØA) to 8 bit, disable flag and select port (ØX1X-XXXX). After initializing or any write to \$C7ØA to change ports a period of at least 2Øus must be allowed before valid data is available at \$C7Ø8. Thereafter, the data will always be valid and updating.

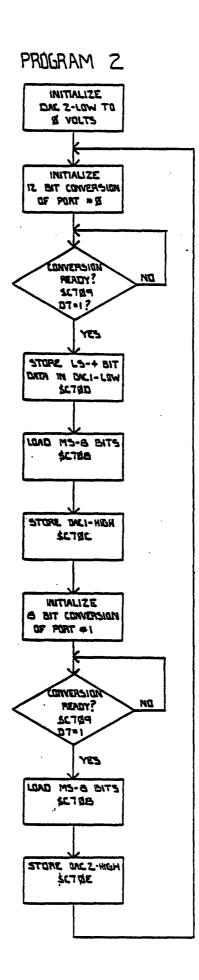

Control of the two 12 bit D/A converters is handled by simply storing data in two buffers for each A/D.

The least significant four bits are stored in a hardware buffer and are not presented to the D/A until the MS eight bits are written. A 12 bit word would be written to DAC1 by writing the LS four bits to \$C70D then the MS eight bits to \$C70C. If 8 bit operation is desired, the LS four bits should be initialized once at the beginning of the program and, thereafter, only the MS eight bits would be written to \$C70C. DAC2 operation is identical, with the LS four bit buffer at \$C70F and the MS eight bit buffer at \$C70E. The DAC order of magnitude is D7=MSB (most significant bit) and D0=LSB (least significant bit).

# Audio Demonstration

An interesting experiment or demonstration of the audio processing capability of the CA-22 would be to connect the output of the preamplifier from a radio, tape player, etc., to an input of the CA-22 then one of the D/A outputs to the input of an audio amplifier. A simple program could then be used to simply 'pass' the converted audio data from input to output of the analog board. If good quality audio equipment is used in this experiment the high fidelity capability of the CA-22 will be realized. Connect the preamplifier output to Port #Ø at J2 Pin 1 and the ground to  $(J_2)$  Pin 2 (use shielded cable). Connect the audio amplifier to DAC1 at J2 Pin 12 and the ground to J2 Pin 11 (use shielded cable). The program found in this manual (PROG. 1) should then be executed and the audio adjusted to a suitable level. Prog. 1 instructs the A/D to do 12-bit conversions of the audio signal then transfers the digital encoded audio data to DAC1 for conversion back to This program could be easily modified to perform 8 bit audio. conversions. Change the #\$80 in line 200 to #0 and delete line 280. Both of the above programs use the flag mode. In 8-bit audio processing the flag is not usually required. To convert Prog.1 to 8-bit mode using no flag change the #\$80 in line 200 to #\$20, delete lines 220, 260, 270, and 280. The label "LOOP" should be inserted in line 290. The FSR (full scale range) of the A/D and D/A may have to be lowered for this experiment.

Jetite or Je 7 J& Feb26, .

| 10  |             | j :+::fe::fe::fe::fe::fe::fe::fe:       | fe :  | ****                                      |  |

|-----|-------------|-----------------------------------------|------------------------------------------|-------------------------------------------|--|

| 20  |             | ; :4:34:                                | PROG. 1                                  | -4e =4e                                   |  |

| 30  |             | ; ::::::::::::::::::::::::::::::::::::: | *****                                    | k she she she she she she she she she     |  |

| 40  |             | ; ** A/D                                | D/A SAMPLE                               | PROGRAM **                                |  |

| 50  |             | ; ** READ                               | ANALOG INP                               | PUT PORT 0**                              |  |

| 60  |             | ; ** AND                                | OUTPUT TO D                              | DAC 1 12 **                               |  |

| 70  |             | ; ** BIT                                | RESOLUTION.                              | REPEAT **                                 |  |

| 80  |             | j :- : te ste ste ste ste ste ste ste   | de sde sde sde sde sde sde sde sde sde s | ie zde zde zde zde zde zde zde zde zde zd |  |

| 90  |             | ;                                       |                                          |                                           |  |

| 100 | C708=       | ADHIGH=\$C                              | 703 A/                                   | YD MS(8) BITS (D7)=MSB                    |  |

| 110 | C709=       | ADLOW ≖\$C                              | 709 A/                                   | 'D LS(4) BITS & FLAG (D0)⊐LSB             |  |

| 120 | C70A=       | CONTRL=\$C                              | 70A CO                                   | DNTROL REGISTER WRI/ONLY                  |  |

| 130 | C70C= .     | DAC1H =\$C                              | 70C D/                                   | A(1) MS(8) BITS & WORD STRB               |  |

| 140 | C70D=       | DAC1L =\$C                              | 70D D/                                   | A(1) LS(4) BIT BUFFER                     |  |

| 150 |             | \$                                      |                                          |                                           |  |

| 160 | 4000        | *=                                      | \$4000 OB                                | BJECT CODE DESTINATION                    |  |

| 170 |             | 1                                       |                                          |                                           |  |

| 180 |             | j stente:                               | ** INITIALI                              | [ZE ****                                  |  |

| 190 |             | \$                                      |                                          |                                           |  |

|     | 4000 A980   | START LDI                               | 7 #\$80                                  | 12 BIT, FLAG ENABLE, PORT(0)              |  |

| 210 | 4002 800RC7 | STI                                     | A CONTRL                                 | INITIALIZE PARAMETERS                     |  |

| 220 | 4005 8D0AC7 | ST                                      | A CONTRL                                 | FORCE NEW CONVERSION                      |  |

| 230 |             | ذ                                       |                                          |                                           |  |

| 240 |             | j ofester                               | ** MAIN BOD                              | ) イ ・*****                                |  |

| 250 |             | <b>;</b>                                |                                          |                                           |  |

| 260 | 4008 AD09C7 | LOOP LD                                 | A ADLOW                                  | GET CONVERSION STATUS                     |  |

| 279 | 4008 10FB   | BP                                      | _ LOOP                                   | IF (D7)=0 NOT READY                       |  |

| 280 | 400D 8D0DC7 | ST                                      | A DAC1L                                  | STORE VALID DATA DAC BUFFER               |  |

| 290 | 4010 AD03C7 | LDI                                     | ADHIGH                                   | GET MS(8) BITS                            |  |

| 300 | 4013 8D0CC7 | ST                                      | 9 DAC1H                                  | AND STROBE DAC W/12 BIT DATA              |  |

| 310 | 4016 400840 | JM                                      | P LOOP                                   | GO DO IT AGAIN                            |  |

·,

Ę

-

•

•

-22-

•

# PROGRAM 1

WHEN STATUS RELISTER (SCTØ9) IS READ AND D7=1 (READY) THE LEAST SIGNIFICANT 4 BITS OF A 12 BIT LONVERSION ARE VALID AND RETURNED IN THE SAME READ CYCLE

|                 | 10  |                  | j           | نیک میک میک میک میک میک میک میک میک میک م |                                          |                                     |     |

|-----------------|-----|------------------|-------------|-------------------------------------------|------------------------------------------|-------------------------------------|-----|

| C               | 20  |                  |             | ** PROG                                   |                                          |                                     |     |

| ×.              | 30  |                  | •           |                                           |                                          |                                     |     |

|                 | 40  |                  | د           | ** AZD DZA SA                             |                                          |                                     |     |

|                 | 50  |                  |             | ** READ ANALO                             |                                          |                                     |     |

|                 | 60  |                  | •<br>•      |                                           | D OUTPUT TO**                            |                                     |     |

|                 | 70  |                  | د           |                                           | BIT RESOLU-**                            |                                     |     |

|                 | 80  |                  | د           |                                           | INPUT PORT1**                            |                                     |     |

|                 | 90  |                  | •           |                                           | TO DAC(2) **                             |                                     |     |

|                 | 100 |                  | د           | ** 8 BIT RESO                             |                                          |                                     |     |

|                 | 110 |                  | •           | ** REPERT END                             |                                          |                                     |     |

|                 | 120 |                  | ۰<br>۰      |                                           |                                          |                                     |     |

| •               | 130 |                  | •           |                                           | 1 - 34 - 34 - 34 - 34 - 34 - 34 - 34 - 3 | •                                   |     |

|                 |     | C708=            | )<br>ODUTCI |                                           | AND MELON DT                             |                                     |     |

|                 |     | C709=            |             | 1=\$C708<br>=\$C709                       | A/D MS(8) BI                             | TS & FLAG (D0)=LSB                  |     |

|                 |     | C708=            |             | _=\$C70A                                  |                                          | STER WRI/ONLY                       |     |

|                 |     | C708=            | IOUT        | =\$C70B                                   | 6 BIT DIGITA                             |                                     |     |

|                 |     | C70C=            |             | =\$C70C                                   |                                          | BITS & WORD STRB                    |     |

|                 |     |                  |             |                                           | D/R(1) HS(8)                             |                                     |     |

|                 |     | C70D=            |             | =\$C70D                                   |                                          |                                     |     |

|                 |     | C70E=            |             | =\$C70E                                   |                                          | BITS & WORD STRB                    |     |

|                 |     | C70F=            |             | =\$C70F                                   | D/R(2) LS(4)                             | DII DUFFER                          |     |

|                 | 220 | 4000             | ذ           |                                           | OBJECT CODE                              | NECTTHOTICH                         |     |

|                 | 240 | 4000             |             | *=\$4000                                  | OBJECT CODE                              | DESITINGITUN                        |     |

|                 | 250 |                  | ;           | **** INITIAL                              | T75                                      |                                     |     |

|                 | 260 | 4000 A90F        | ;<br>INIT   | LDR #15                                   |                                          | DAC2 LS(4) BITS                     |     |

| -               | 270 | 4002 8D0FC7      | THTI        | STA DAC2L                                 | TO (07)                                  | . DACE 23(4) 8113                   |     |

|                 | 280 |                  |             | STA DACEL                                 | 10 (097                                  |                                     |     |

| N.              | 290 |                  | ة           | **** MAIN BO                              | DY ****                                  |                                     |     |

|                 | 300 |                  | د<br>ب      | ***** IIFITIA DC                          |                                          |                                     |     |

|                 |     | 4005 A980        | START       | LDA #\$80                                 | 12 BTT. 51 8                             | G ENABLE, PORT (0)                  |     |

|                 | 320 | 4007 202140      | OT HAT      | JSR RDY                                   |                                          | IND GET RDY FLAG                    | • • |

| •               |     |                  |             | STA DAC1L                                 |                                          | BITS DAC(1)                         |     |

|                 |     | 400D 8003C7      |             | LDA ADHIGH                                |                                          | BITS PORT(0)                        | -   |

|                 |     | 4010 8D0CC7      |             | STA DAC1H                                 |                                          | 2 BIT DATA                          |     |

|                 |     | 4013 8901        |             | LDA #1                                    |                                          | ENABLE, PORT(1)                     |     |

|                 |     | 4015 202140      |             | JSR RDY                                   |                                          | IND GET RDY FLAG                    |     |

|                 |     | 4018 RD08C7      |             | LDA ADHIGH                                |                                          | BITS PORT(1)                        | -   |

|                 |     | 4018 8D0EC7      |             | STA DAC2H                                 |                                          | 2 BIT DATA                          |     |

|                 |     | 401E 4C0540      |             | JMP START                                 | & GO DO IT                               |                                     |     |

| · • ·           |     | 4021 8D0AC7      | RDY         | STA CONTRL                                | -                                        | TERS AND PORT #                     |     |

|                 |     | 4024 8D0AC7      | RUT         | STA CONTRL                                |                                          | CONVERSION                          |     |

| <b>**</b> 5 4 5 |     | 4027 AD09C7      | LOOP        | LDA ADLOW                                 |                                          | ERSION STATUS                       |     |

|                 |     | 4028 10FB        |             | BPL LOOP                                  | IF D7=0 NO                               |                                     |     |

|                 |     | 4020 60          |             | RTS                                       |                                          | LID DATA!-RETURN                    | -   |

|                 |     | 7 <b>5</b> 20 00 |             | in i 🖌                                    | ME 007E 90                               | tanana (" (") ())), "Σ(ang )(())()) |     |

•

.

-25-

1 GOTO 10 2: 3: PROG. 3 5 : D. C. D. V. M PROGRAM USING 574 7 : CAN ALSO BE USED TO ADJUST GAIN 8 : AND OFFSET USING 4 1/2 DIGIT D. V. M. 9 : 10 A=50952: REM ADDRESS OF A/D 15 R=20/4096: REM RESOLUTION=20 VOLTS SCALE / 12 BIT(21N) 20 POKEA+2, 128: REM SET UP PORT AND BITS AND ENABLE 23 : 25 FOR LOOP=1T020: REM TAKE AVERAGE OF READING TO PREVENT JITTER 30 H=PEEK(A+1): I=H: REM CHECK FOR CONVERSION READY 40 H=HAND128: IFH<>128 GOTO 30: REM IF D7=0 NOT READY 60 J=IAND15: REM GET LS(4) BITS 70 V=PEEK(A): REN GET MS(8) BITS 80 V=V\*16+J: V=V\*R: REM MULTIPLY BINARY EQUIV. X RESOLUTION=VOLTS(ABS) 90 X=10-V: VX=VX+X: NEXT LOOP: X=VX/20: REM AVERAGE 95 X=X\*1E3: X=INT(X): X=X/1E3: REM WE ONLY WANT 3 DIGIT FRACTION 100 PRINTCHR\$(13); TAB(5); X; TAB(13); "VOLTS"; : REM DISPLAY VOLTAGE 110 VX=0: GOT025: REM CLEANUP AND RESTART

574 I/O Assignment

4

| WO-\$C7ØF  | - | DAC2 LOW 4 BITS                                   |

|------------|---|---------------------------------------------------|

| WO-\$C7ØE  | - | DAC2 HIGH 8 BITS + WORD STROBE                    |

| WO-\$C7ØD  | - | DAC1 LOW 4 BITS                                   |

| WO-\$C7ØC  | - | DAC1 HIGH 8 BITS + INTENSITY OUTPUT + WORD STROBE |

| WO-\$C7ØB∙ | - | 6 BIT I/O OUT                                     |

| WO-\$C7ØA  | - | CONTROL REGISTER (MUX., INT., BITS)               |

| RO-\$C7Ø9  | - | ADLOW - 4 BITS + FLAG = 3T <sup>2</sup> L INPUTS  |

| RO-\$C7Ø8  | - | ADHIGH - 8 BITS + (RESET UPDATE CONTROL)          |

|        | 7                                  | 6          | 5                | 4      | 3        | 2        | l        | ø_       |                      |

|--------|------------------------------------|------------|------------------|--------|----------|----------|----------|----------|----------------------|

| \$C7Ø9 | l=VALID<br>A/D DATA                | IOLN6      | IO1N5            | IOLN4  | AD3      | AD2      | AD1      | ADØ      | STATUS/DATA REGISTER |

| \$C7Ø8 | AD11                               | ADLØ       | AD9              | AD8    | AD7      | AD6      | AD5      | AD4      | DATA REGISTER        |

| \$C7ØA | Ø=8 BIT<br>1= 12 BIT<br>CONVERSION | l<br>ENINT | Ø=FLAG<br>ENABLE | X<br>X | MD<br>MD | MC<br>MC | MB<br>MB | Ma<br>Ma | CONTROL REGISTER     |

| \$C7Ø8 | = | 5Ø952 | \$C7ØC | =  | 5Ø956 |

|--------|---|-------|--------|----|-------|

| \$C7Ø9 | = | 50953 | \$C7ØD | =  | 50957 |

| \$C7ØA | = | 5Ø954 | \$C7ØE | =` | 5Ø958 |

| \$C7ØB | = | 50955 | \$C7ØF | =  | 5Ø959 |

#### Applications Information

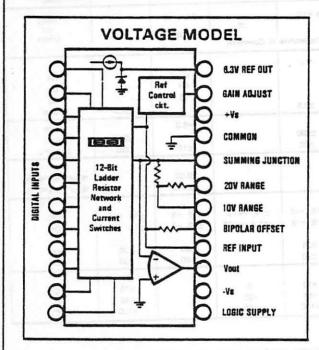

#### D/A Converters

The Digital to Analog converters are high speed devices capable of FSR swing in under one usecond settling to .01% FSR in two useconds. This includes switching, slewing, and settling time. In most cases, the D/A converter speed will be limited only by the processing speed of the host computer. The loading of the output op-amps should be kept above 1500 ohms during normal operation. The output may be shorted to either supply rail or ground indefinitely without damage to the device.

#### A/D Converter

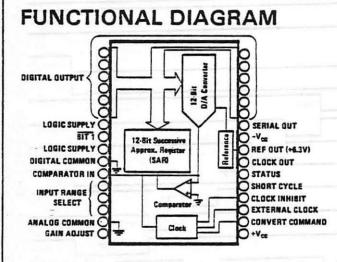

The A/D converter is a high speed, highly accurate successive approximation device.

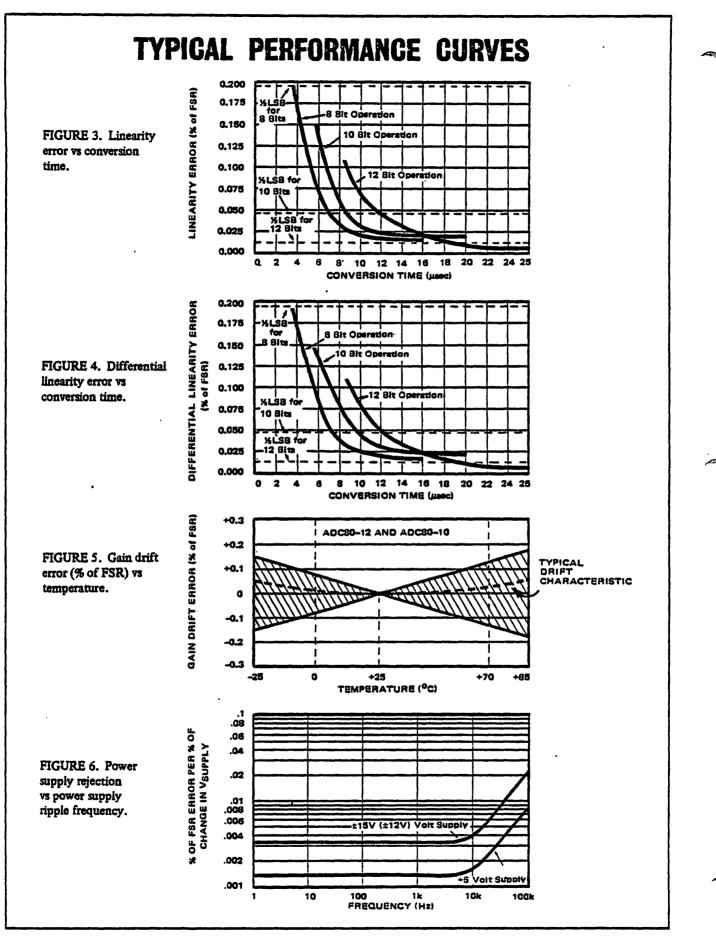

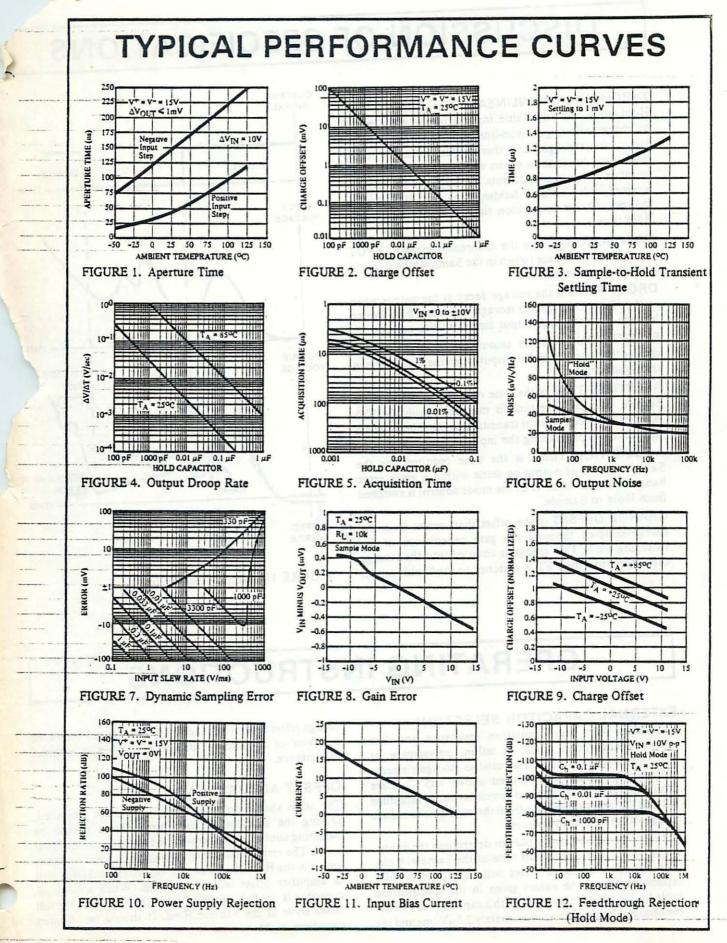

As shipped from the factory the A/D will do approximately 66,000 8-bit and 28,000 12-bit conversions per second. If the application does not require exacting accuracy, the conversion rates may be increased several different ways. The following paragraphs may be used by the technically oriented user to customize the error vs conversion rate for his particular application if so desired.

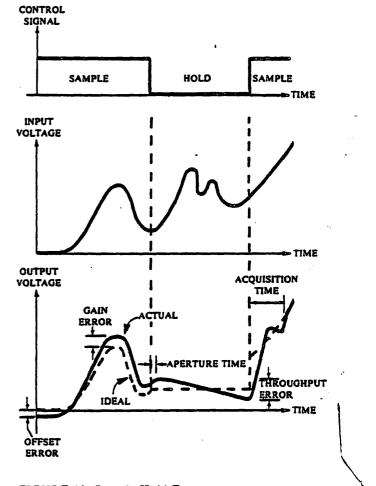

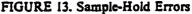

The A/D converter is comprised of a 16-channel multiplexer, a sample and hold amplifier and the converter itself. The major factors in this sequence of analog acquisition are multiplexer switching time of 1.5 usec (if a new port has just been selected), the sample time of the S/H amp (8 usec @ .01% error) and the actual A/D conversion rate. It can be seen that if any of these factors can be decreased the conversion rate will increase accordingly.

-28-

The most obvious way to increase throughput would be to delete the S/H amp entirely and decrease the timing components R85 and C25 to about 1 usec. This would also require a jumper from the sample and hold Pins 8 to 5 after removing the component.

Since the 12-bit conversion takes approximately 25 usec and the 8-bit approximately 5 usec, it can be seen that a dramatic conversion rate increase will be obtained, particularly in the 8-bit mode where the sample time is actually longer than the conversion time. Unfortunately, in most applications, the S/H will be required to prevent the converter from converting one voltage on the MSB's and an unrelated voltage on the LSB's, the error depending on the slew rate of the input vs the conversion rate of the A/D. This type of error can be quite large and is not a recommended tactic in most applications.

Another way to increase the conversion speed slightly less than the previous example but with good accuracy results would be to decrease the sample time allowed the S/H amp. As shipped, the S/H amp is adjusted to an 8 usec window which translates to .01% sample error. If a larger error can be tolerated, this can be adjusted to 6 usec for .1% error or 4 usec for 1% error. Four usec is about the minimum sample window that should be allowed as the percentage of error will increase dramatically with any further increase, unless the hold capacitor is reduced in size accordingly. Consult manufacturer's specifications for these values.

The previous methods are valid in the 8-bit and 12-bit mode. In the 8-bit mode the actual conversion time of the A/D itself may be adjusted. This would be accomplished by substituting the

-29-

crystal (X1) with another value. As shipped from the factory, this frequency is 3579545 Hz resulting in an 8-bit conversion time of 5 usec. The maximum recommended substitution would be 4.5 MHz resulting in 4 usec conversion time and an increase in error rate of approximately +/-%LSB.

The convert command one shot (U4H) 800 nsec pulse is used to insure that the sample to hold transient of the sample/hold amp has settled and in no case should this be adjusted below 800 nsec. In applications where the ambient temperature approaches or exceeds  $50^{\circ}$ C, it may be beneficial to increase this time to 1.2 usec.

As can be seen from the previous discussion, trade offs can be made to increase the speed of data acquisition if slightly more error can be tolerated. Conversely, if greater accuracy is desired, conversion rates can be sacrificed to decrease the error. Although in most applications the 574 is already optimized as shipped from the factory. The sample "window" could be increased with about 10 usec giving the highest degree of accuracy and a 2 MHz crystal substitution for (X1) would increase converter accuracy to its highest capabilities, but resulting in conversion times of 9 usec + 10 usec + 800 ns = 19.8 usec. The resulting accuracy improvement in most applications would not be required.

-30-

### Scaling

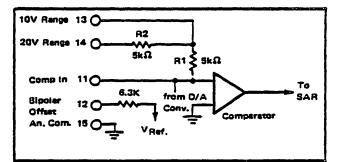

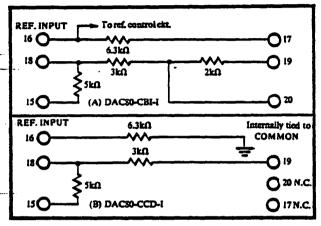

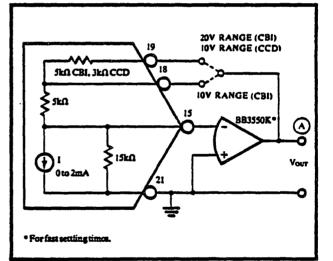

The ADC80 input and DAC80 outputs should be scaled as close to the maximum signal range as possible in order to utilize the maximum signal resolution of the converters.

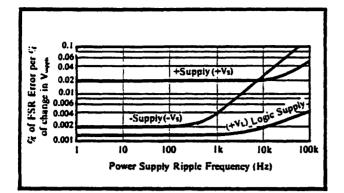

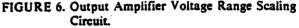

It is recommended that output voltage ranges -10 to +10V and 0 to +10V not be used if the supply voltages are ever less than the recommended  $\pm 12V$ . The output amplifier may saturate if Vsupply -Vout > 2.0V. Refer to Figure 1 for possible scaling ranges and procedures. The 574 is factory configured for (C0B) code  $\pm -10V$ .

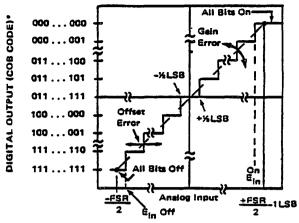

### Digital Input Codes

Three binary codes are available on the 574 analog interface. They are complementary (logic "Ø" is true), straight binary (CSB) for unipolar input signal ranges, and complementary two's complement (CTC) and complementary offset binary (COB) for bipolar input signal ranges.

| Binary               |                    | Vo             | oltage Range        | and LSB Value     | S                   |                   |

|----------------------|--------------------|----------------|---------------------|-------------------|---------------------|-------------------|

| Voltage Range        | Defined As         | +/-1ØV         | +5V                 | +/-2.5V           | Ø to lØV            | Ø to +5V          |

| Code                 |                    | COB<br>or CTC* | COB<br>or CTC*      | COB<br>or CTC*    | CSB**               | CSB**             |

| One Least            | FSR/2 <sup>N</sup> | $20^{N}$       | $1 \text{øv}/2^{N}$ | 5v/2 <sup>N</sup> | $1 \text{øv/2}^{N}$ | 5v/2 <sup>N</sup> |

| Significant          | N=8                | 78.13mV        | 39.06mV             | 19.53mV           | 39.06mV             | 19.53mV           |

| Bit                  | N=12               | 4.88mV         | 2.44mV              | 1.22mV            | 2.44mV              | 1.22mV            |

| Transition<br>Values |                    |                |                     |                   |                     |                   |

| ØØØØØØ***            | +Full Scale        | +1ØV-3/2LSB    | +5V-3/2LSB          | +2.5-3/2LSB       | +1ØV-3/2LSB         | +5V-3/2LSB        |

| Ø11111               | Mid Scale          | ø              | ø                   | ø                 | +5V                 | +2.5V             |

| 11111ø               | -Full Scale        | -1ØV+1/2LSB    | -5V+1/2LSB          | -2.5+1/2LSB       | Ø+1/2LSB            | Ø+1/2LSB          |

|                      |                    |                |                     |                   |                     |                   |

.

| *COB =  | Complementary Offset Binary       | ***Voltages given are the nominal |

|---------|-----------------------------------|-----------------------------------|

| **CSB = | Complementary Straight Binary     | value for transition to the code  |

| *CTC -  | - Complementary Two's Complement. | specified.                        |

|         | Obtained by using the complement  |                                   |

|         | of the most significant bit.      |                                   |

. 1

\*

Figure 1.

.

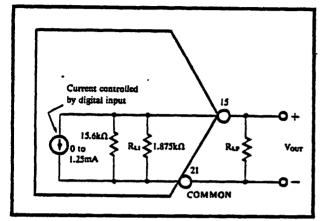

### A/D Converter Ranges

| Input Range | Code        | W3Ø | W31 | W27 | W28 | W29 |

|-------------|-------------|-----|-----|-----|-----|-----|

| +/-1ØV*     | *COB or CTC | х   |     |     | X   |     |

| +/-5V       | COB or CTC  |     | х   |     | X   |     |

| +/-2.5V     | COB or CTC  |     | х   | Х   | Х   |     |

| Ø to +5V    | CSB         |     | х   | Х   |     | Х   |

| Ø to +1ØV   | CSB         |     | Х   |     |     | X   |

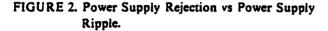

X = Jumper: All others should be unconnected. \*As shipped from Factory. Refer to Sheet 2 of Schematics.

Figure 2.

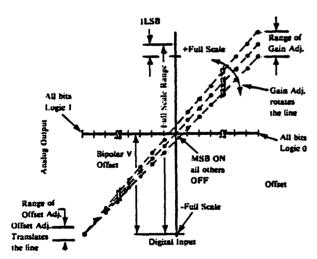

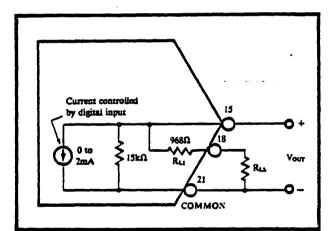

## D/A Converter Ranges

| Range     | Code        | Pin 6<br>Op Amp | Pin 17<br>D/A | Pin 19<br>D/A |

|-----------|-------------|-----------------|---------------|---------------|

| +/-1ØV*   | *COB or CTC | 19 D/A          | 15 D/A        | 6 OP-AMP      |

| +/-5V     | COB or CTC  | 18 D/A          | 15 D/A        | N.C.          |

| +/-2.5V   | COB or CTC  | 18 D/A          | 15 D/A        | 15 D/A        |

| Ø to +1ØV | CSB         | 18 D/A          | 21 D/A        | N.C.          |

| Ø to +5V  | CSB         | 18 D/A          | 21 D/A        | 15 D/A        |

\*As shipped from Factory. Refer to Sheet 3 of Schematics.

Figure 3.

-33-

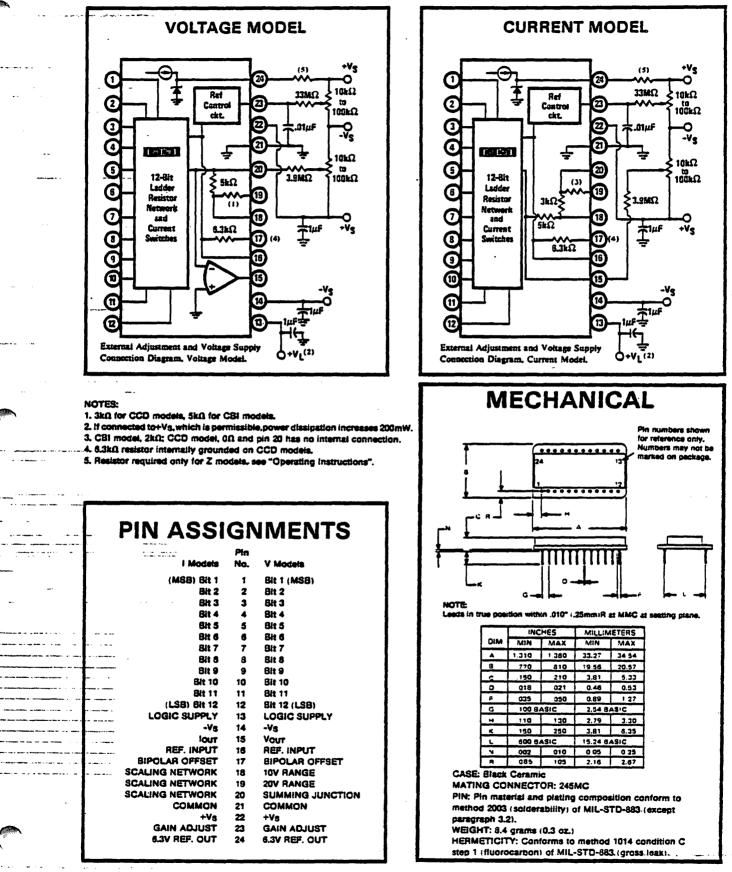

### Digital I/O

The CA-22 as delivered by the factory has a 6-bit digital output port and a 3-bit digital input port. Both are TTL compatible and may be used in applications requiring logical control or enabling of a device to which the CA-22 is interfaced. If more than three input lines are required or if the signal is not (TTL) compatible and all 16 multiplexed analog inputs are not required in the application, they may be used to 'read' those digital inputs. The absolute maximum input rating (+/-25V) of the multiplexer must be observed in this case.

The 6-bit output port is configured by the factory as TTL compatible. The user may reconfigure this to several different modes of interfacing.  $\emptyset.7V$  to +12V interfacing may be accomplished by cutting W-23 and jumpering W-24 or .7 to 30V open collector by cutting out R49-R54. The 7406 open collector driver is capable of sinking 40 MA and will tolerate a high level output voltage up to +30V.

The 6-bit output port may be expanded to 8-bit by populating the prototyping area of the CA-22 if required.

Refer to the software section for Digital I/O techniques of these two ports.

Note that the 6-bit output port is inverted data. UlD may be substituted with a 7407, 7417 or equivalent part if necessary to change to true data.

-34-

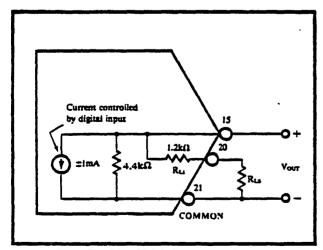

### X-Y Oscilloscope Plotting

An oscilloscope with an X-Y plotting function and intensity input may be used for visual display of the X-Y outputs of the two DACs on the 574. UlC (Sheet 3) is used to control the intensity of the beam.

The interface should be used such that DAC'2 then DAC'1 are updated in that sequence. When DAC'1 is updated U1C Pin 12 one-shot is fired which will be the approximate settling time of DAC'1. After this period U1C Pin 13 is fired and is used to (unblank) the oscilloscope beam. This signal is factory configured for low true blank (positive logic). If your oscilloscope requires high true blank, cut W-39 and jumper W-40. R32 may be used to vary the "unblank" period but in some applications C15 and/or R34 may need optimization by the user for his application or scope persistence.

### Adjustments

Although calibration with lower resolution equipment is possible, a 4½ digit D.V.M. should be used for the following procedures.

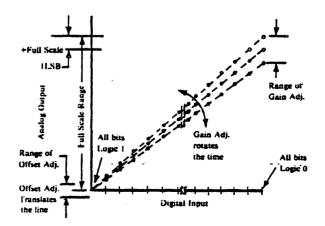

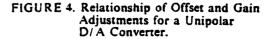

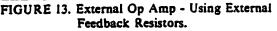

### D/A Offset Adjustments

For unipolar (CSB) configurations, apply the digital input code that should produce zero potential output and adjust the offset potentiometer for zero output.

For bipolar (COB,CTC) configuration, apply the digital input code that should produce the maximum negative output voltage and adjust the offset potentiometer for that voltage.

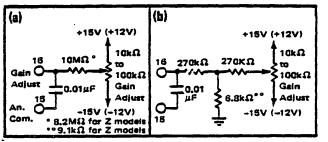

### D/A Gain Adjustments

For either unipolar or bipolar configurations, apply the digital input that should give the maximum positive voltage output for the range you have configured. Adjust the gain potentiometer for this positive full scale voltage. Since the gain and offset adjustments affect each other, this procedure may have to be repeated several times to get the best results.

### A/D Offset Adjustment

Sweep the input through the end point transition voltage that should cause an output transition to all ones. Adjust the offset potentiometer R4 until the actual end point transition voltage occurs at E off/on. The ideal transition voltage values of the input are given in Figure 1.

#### A/D Gain Adjustment

Sweep the input through the end point transition voltage that should cause an output transition to all zeros. Adjust

-36-

the gain potentiometer R3 until the actual end point transition occurs at E on/off. Figure 1 details the transition voltage levels required.

R6Ø has been provided to facilitate sweeping the analog input voltage during these adjustments.

Since the gain and offset adjustments affect each other, this procedure may have to be repeated several times to get the best results.

### Theory of Operation

### Analog to Digital Data Acquisition

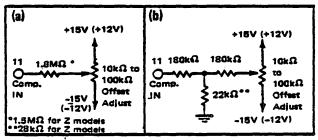

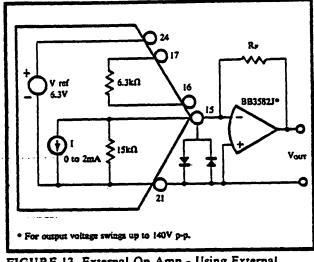

The ADC is a successive approximation type converter which requires no software overhead during the conversion Data acquisition is accomplished in the following process. manner. Port selection (1 of 16), conversion resolution (8 or 12-bit) and flag/no flag are selected by the user by a write to \$C70A which is decoded as (/FORMAT). This 'word' is latched into U2C which controls the 'format' of the data acquisition. MA-MD select the proper port through the multiplexers UlA and U2A. Rl and R2 prevent excessive current flow through the multiplexer in an overvoltage situation. The absolute maximum input should be kept less than +/-25 volts. D1 and D2 prevent more than +/-.75V of the rails of the analog supply voltage grom being applied to the sample and hold (S/H) amplifier. Rll and Rl2 form the offset adjustment network. R5 controls the percentage of adjustment capability of the gain network R5, R6, R7 and R3. Cll prevents noise from being injected into the gain input. C31, C28, C30, C29, C13, C14, C4, C3, C29, C28, C1Ø and C8 are for power supply decoupling and high frequency filtering. Cl2 is the hold capacitor of the S/H.

A typical cycle involves the following. The one shot U4H causes the S/H to switch to the sample mode for 8 usec. At the end of this period the S/H is switched to HOLD and the one shot U4H Pin 5 is triggered. On the trailing edge of this delay (sample to hold transient settling time) the convert command is generated. At the end of the convert cycle (STATUS) generates

-38-

a new sample and the cycle continues. Until the next (CONV) command data is available at (AD11-ADØ) and on the first (Ø2) the data is latched into the 12-bit buffer U3B and U3A Sheet 1 by setting U4E Pin 5 (EOC) and U4F Pin 5 (VDF) high which are gated through U4G Sheet 1.

This 12-bit buffer will be updated at the completion of every converter cycle unless (FLAG) is high indicating the program has just read the LS(4) bits and flag at \$C709 (/RL). Unable to update the 12-bit buffer at this time the converter will initiate a new cycle so that 'fresh' and updated information will be available after the program reads the MS(8) bits by reading \$C708 (/RH) and reseting the flag register U4F.

When a new (FORMAT) is generated it must also be assumed that a new port has also been selected. When this occurs a new sample is forced by (/SAMPLE) USF Pin 8 through U4G Pin 13. (/SAMPLE) also holds the valid data flag circuitry in the reset state so that when the present cycle is completed (VDF) will not be generated which would enable (FLAG). Since the S/H amp has been switched to sample the present conversion is invalid. At the end of this cycle U5F Pin 8 will be reset and at the end of the next cycle which will contain valid data (VDF) may be generated. If the cycle finishes after the sample time, the (CONV) command will be generated by the converter itself through U4F Pin 6 and the end of conversion latch U4E Pin 6. If the cycle finishes before the sample time the converter will stop and the (CONV) command will be generated by the end of the sample one shot period U4H Pin 4. This prevents wasting

-39-

up to 25 usec after a (/FORMAT) command before a sample could be taken.

The converter has an internal clock reference that is used in the 12-bit mode. In the 8-bit mode an external clock is provided by the crystal reference X1 and U5E and the internal clock must be switched off by (/8BIT) clock inhibit. U4E Pin 9 is used to sync the external clock to the convert command and divide the clock by two resulting in a 50% duty cycle. The conversion rate can be found by 1/((X1/2)/(BITS+1)). Where X1 is the crystal frequency in hertz, BITS equals number of bits of conversion (8). The 8-bit mode is accomplished by enabling the short cycle feature of the converter at Pin 21. Ten bit conversions could be done by connecting U4C Pin 9 to U2B Pin 28 instead of U2B Pin 30.

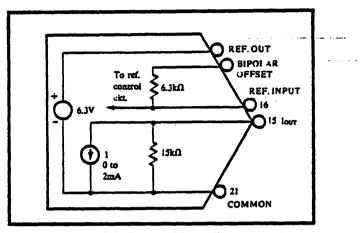

### Digital to Analog Conversion

Refer to Sheet 3 of schematics. Since both DAC's are identical only DAC'l will be discussed. A 12-bit word is written to the DAC in the following manner. The LS(4) bits are first written to U4B and strobed by (/DALL) which was decoded by U5G Sheet 1 as a write cycle to \$C7ØD. Notice that the 12-bit word latched in the 12-bit buffer U4A and U5C is not changed. Therefore, there is no change in the DAC output. To complete the 12-bit write the MS(8) bits are then written to \$C7ØC which is decoded as (/DALH). During this write cycle the MS(8) bits are presented by the CPU and the LS(4) bits are presented by U4B to the 12-bit buffer. At the end of

-40-

this write cycle the full 12-bit word is latched into the 12-bit buffer and presented to the DAC and the corresponding output change, if any, will be output. It can be seen from this discussion that a true 8-bit mode is inherently present and available. If U4B is first initialized to a predetermined offset or  $\emptyset$ V, the MS(8) bits of the 12-bit buffer can then be changed at will with no change in the LS(4) bits as long as no writes are done to \$C7 $\emptyset$ D after software initialization.

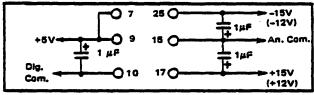

R82 is required in applications using supplies under +/-15 volts to supply the necessary current for the internal reference of the DAC at Pins 24 and 16 of U5B. C31, C32, C40, C39, C48 and C45 are for power supply decoupling and high frequency filtering. C55 and R93 form a compensation network in the op-amp circuit. R76 in the offset circuit is used to increase the resolution of the offset pot R65. R59 is not installed but may be used in conjunction with a resistor installed at W53 after cutting W53 to form a voltage scaling network. In most cases the output should be scaled using the information given in other sections of this manual. R80 controls the percentage of gain adjustability of the network R72, R71, Increasing R80 increases the percentage of adjustability. and R80. C47 prevents noise from being injected into the gain adjust input.

-41-

### Installation

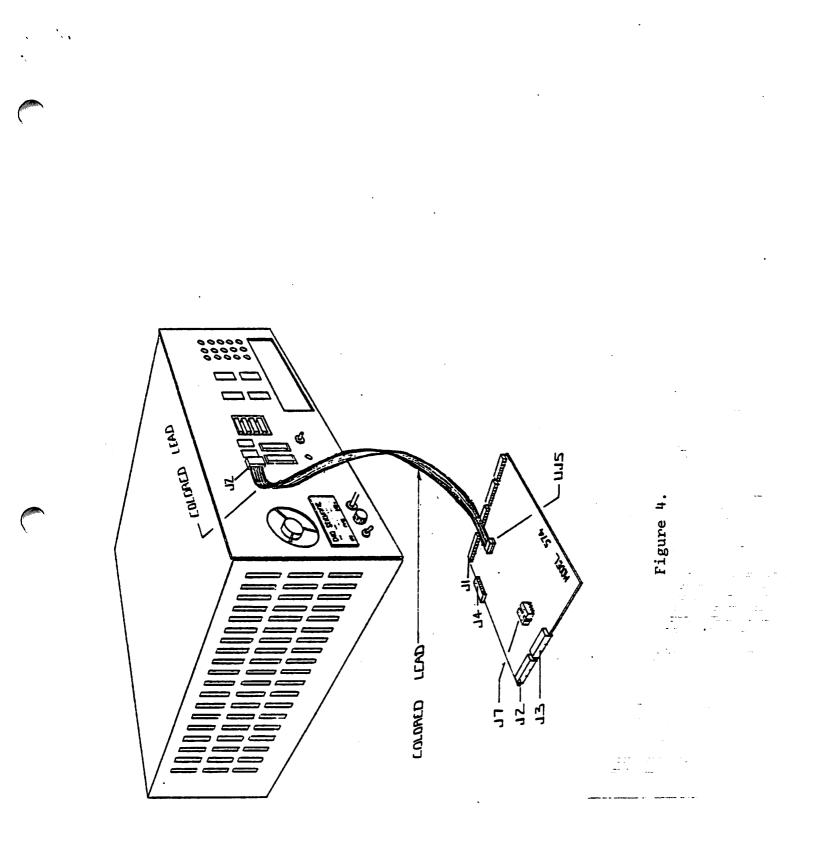

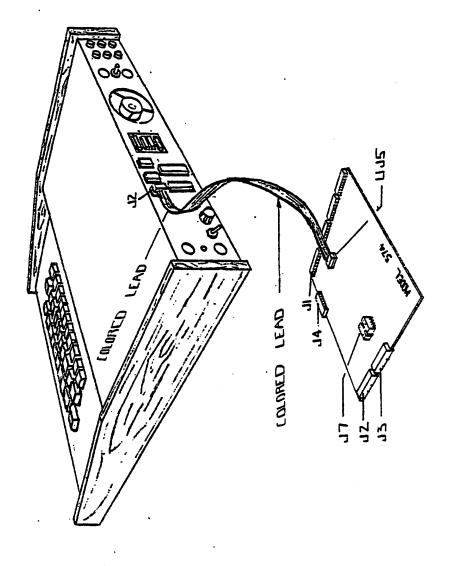

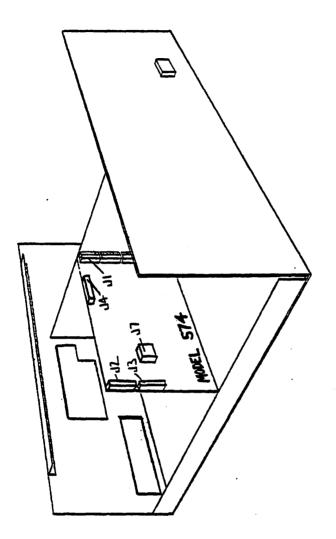

### Accessory Bus C4P-MF, C8P-DF